首页 > 代码库 > [高级篇] 在qucs中使用verilog

[高级篇] 在qucs中使用verilog

为了确保能够正确运行,请确保你现在程序版本为

Qucs 0.0.18

其实将verilog程序放入qucs并不是一件复杂的事情,qucs已经足够简化我们的工作,我们只需要将模块的源代码复制到当前qucs的工作目录下qucs就能进行一系列智能的操作,包括自动添加到工程,以及能够自动识别我们verilog的模块的端口列表。

打开qucs,现在Verilog标签下没有任何文件,我们只需要将我们的verilog的.v文件拷贝过来qucs就能自动识别了。

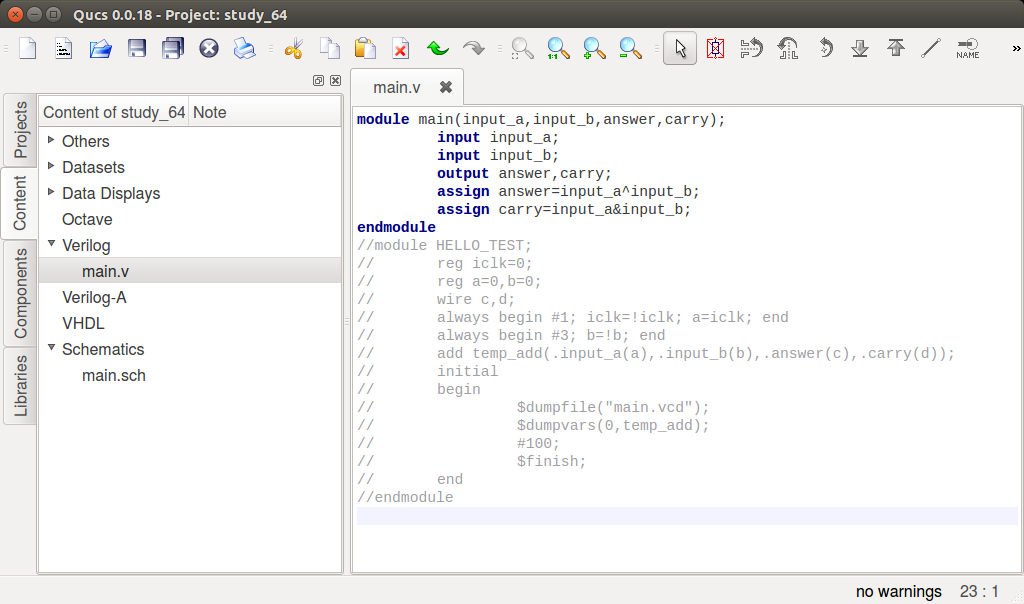

一个verilog的半加器代码,这里verilog标签下已经识别到我们的文件了,如果qucs没有刷新在Projects下重新点击一下工程的名字就能看到文件添加过来了。

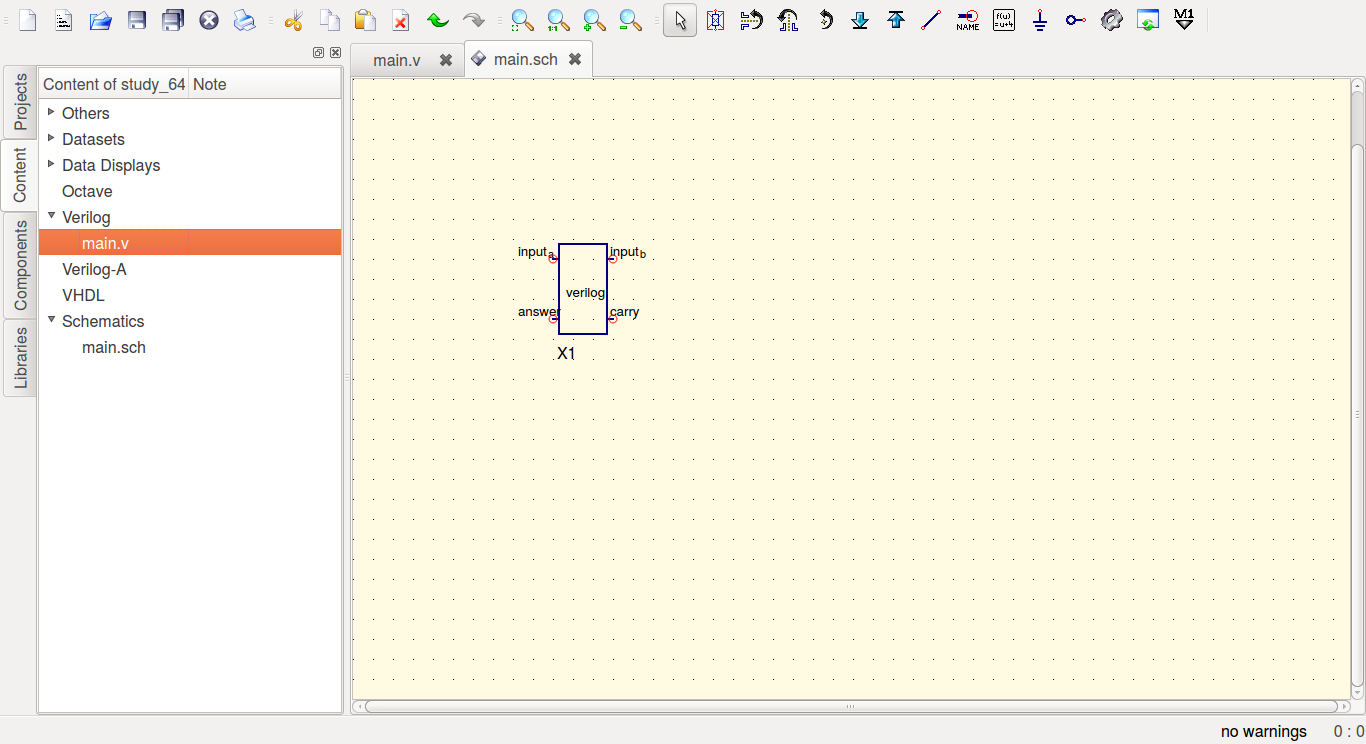

然后鼠标点击一下这个main.v,之后鼠标移到我们的原理图上就会出现一个子电路,四个端口,和我们程序里的两个输入两个输出一致。 qucs非常漂亮!

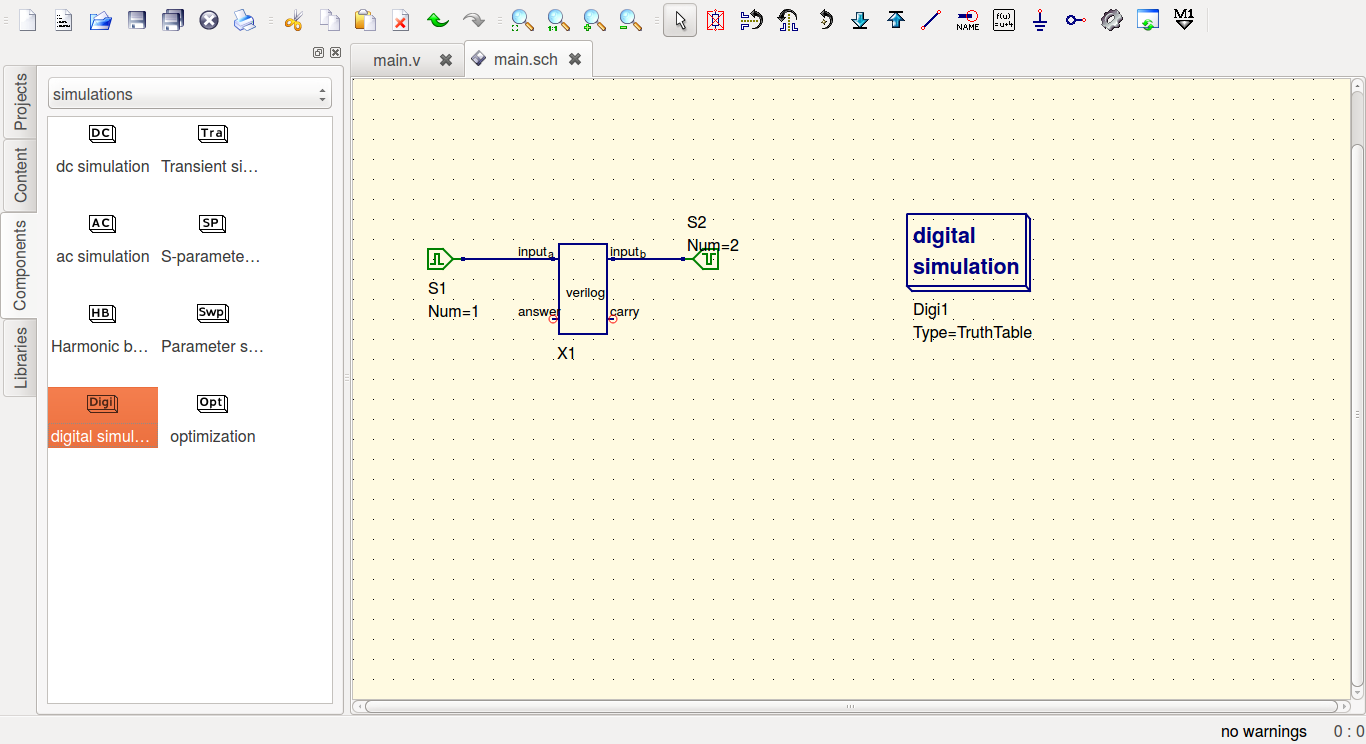

然后我们进行一个数字的仿真.

注意,在digital simulation中我们需要将model的值修改为verilog,因为还有一个选项是VHDL,所以理论上VHDL的代码也能仿真。

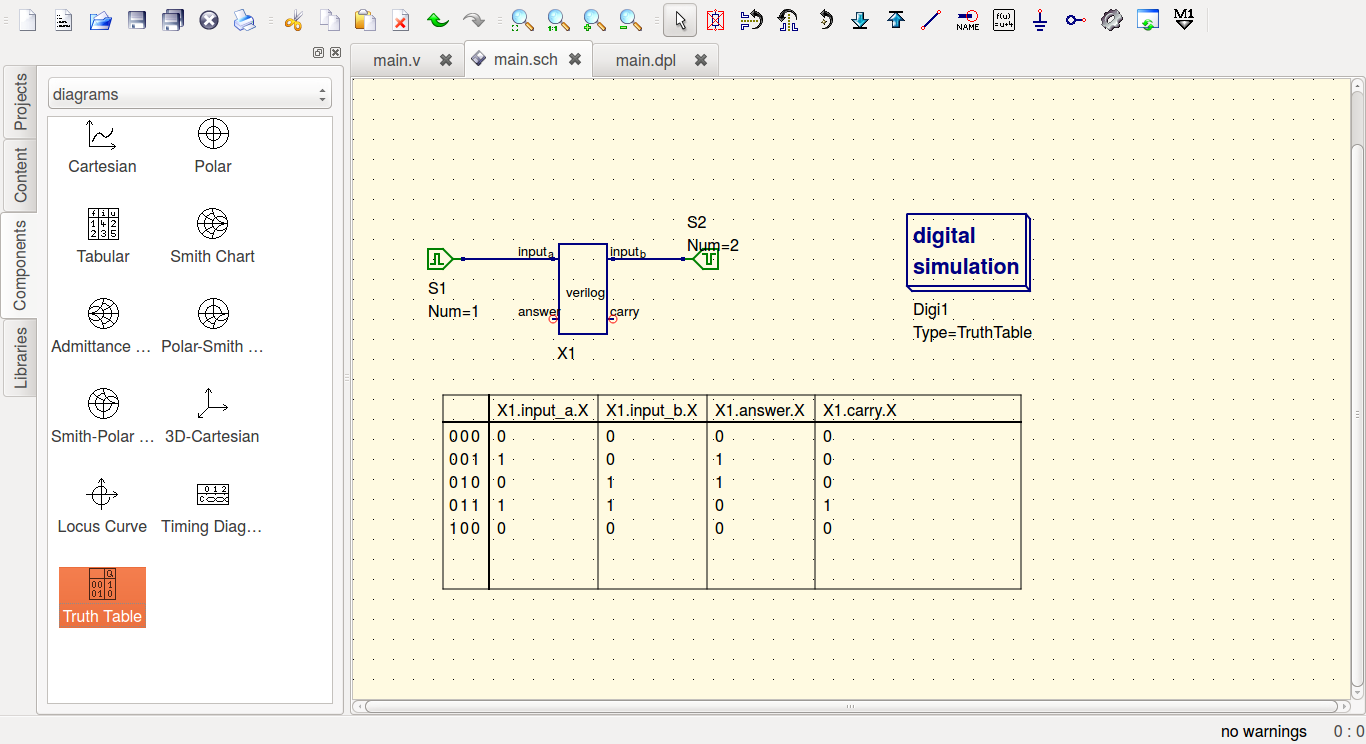

点击OK之后我们就算做好工作了,然后仿真一下,用真值表显示一下我们的半加器是否正确。 qucs 0.0.18的仿真比老版本的快速多 了,而且以前版本偶尔会出现仿真卡住的现象也消失了,新版本做的修改还是挺大的。

这个仿真可以将模块用于电路中,与gtkwave一样是一个不错的工具。

[高级篇] 在qucs中使用verilog

声明:以上内容来自用户投稿及互联网公开渠道收集整理发布,本网站不拥有所有权,未作人工编辑处理,也不承担相关法律责任,若内容有误或涉及侵权可进行投诉: 投诉/举报 工作人员会在5个工作日内联系你,一经查实,本站将立刻删除涉嫌侵权内容。