首页 > 代码库 > Mcspi使用小结

Mcspi使用小结

1、Mcspi控制器结构

Spi总线总共有四根信号线(CLK时钟线,CS片选线,MOSI主设备输出从设备输入线,MISO主设备输入从设备输出线),其工作过程就是,在clk的控制下,主设备和从设备的两个双向移位寄存器进行数据交换。

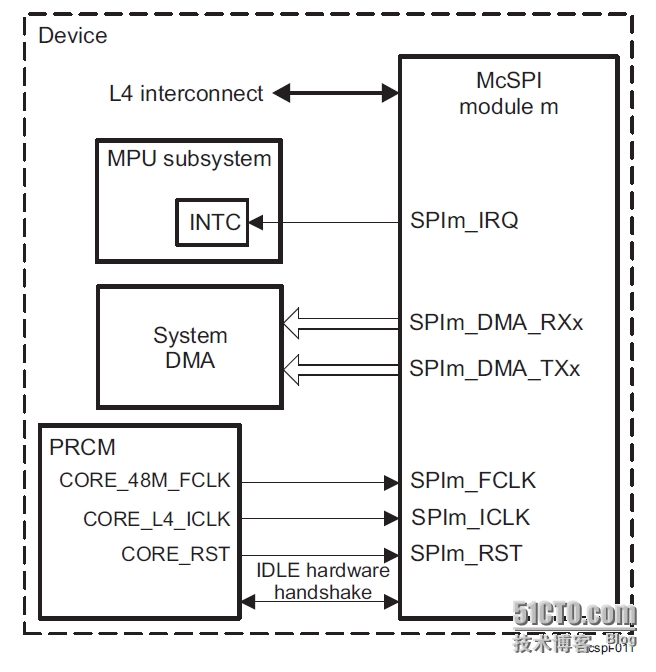

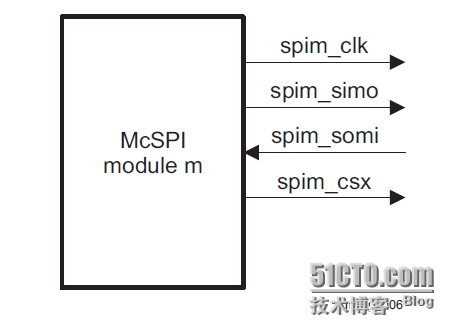

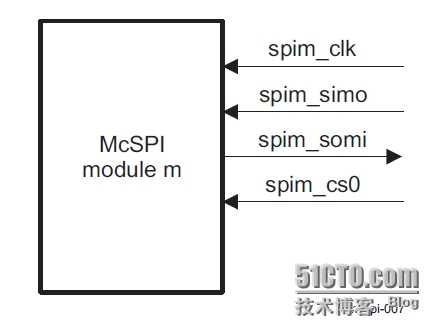

一般CPU内都会集成一个或者多个Mcspi(多通道串行接口)控制器,控制器的内部结构如图1-1所示,一个控制器有一个或者多个通道,每个通道使用独立的寄存器,并且每个通道对应两个DMA请求(读和写),一个INTC中断请求。FCLK是功能时钟,经过分频器为SPI提供工作时钟CLK(分频器的值通过寄存器设置),ICLK是总线时钟,只有该时钟使能才能对Mcspi控制器里的寄存器进行读写。控制器可以配置为主设备或者从设备,如下图1-2和图1-3所示,时钟信号和片选信号由控制器内部提供为主设备,外部提供为从设备。

Mcspi作为主设备时,可以配置成单通道工作和多通道工作。在单通道工作下,片选信号可以配置为自动输出和软件控制输出两种;在多通道工作下,片选信号只能自动输出。

图1-1

图1-2

图1-3

2、Mcspi控制器工作模式

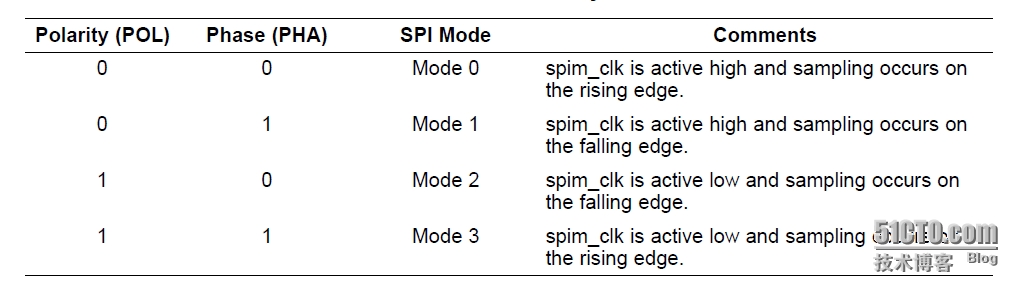

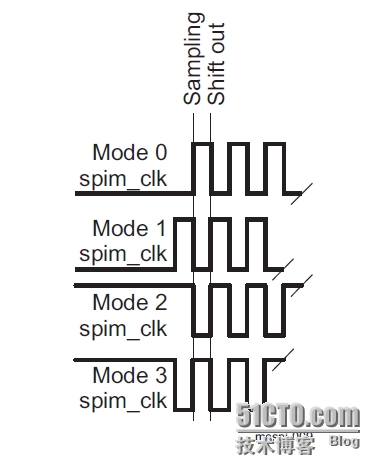

作为主设备的Mcspi控制器,为了和外设进行数据交换,根据外设工作要求,主设备输出的串行时钟的极性和相位可以配置。如图2-1和图2-2所示,共有四种模式。

图2-1

图2-2

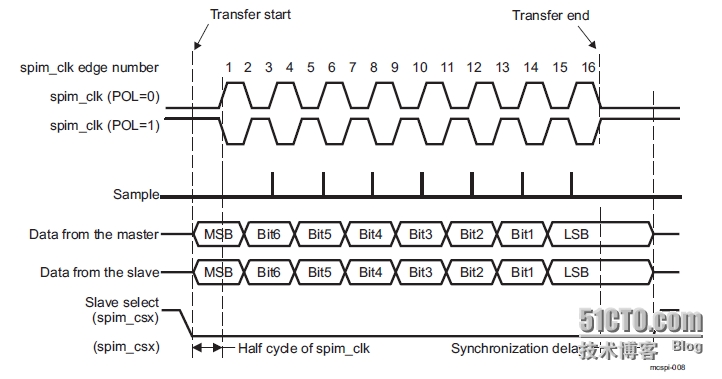

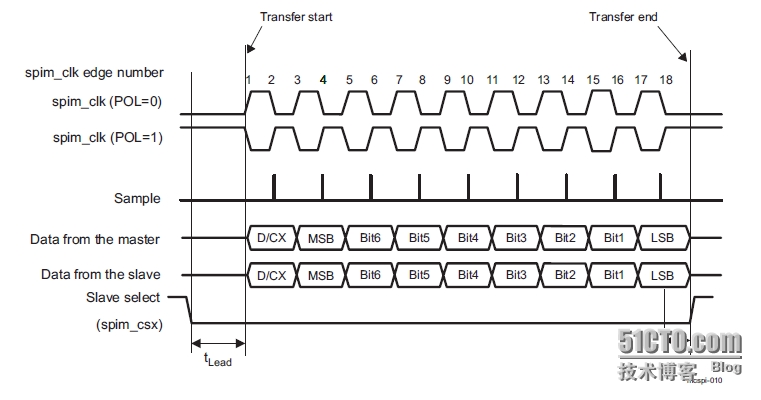

钟极性用来配置同步时钟空闲时的状态,对传输协议没有重大影响,时钟相位则用来配置spi总线的传输协议。如果PHA=0,片选有效后主设备和从设备立刻准备数据(主设备将数据移到MOSI上,从设备将数据移到MISO上),半个时钟周期后输出时钟信号,即在第一个时钟沿对第一位数据进行采样,如图2-3所示;如果PHA=1,片选有效后经过时间tLead开始输出时钟信号(tLead的大小可以通过寄存器配置),同时输出数据,半个时钟周期后数据准备好,即在第二个时钟沿对第一位数据进行采样,如图2-4所示。

图2-3

图2-4

3、使用

在使用时,应该根据从设备支持的模式,将主设备配置成四种模式中的一种。

Mcspi使用小结