首页 > 代码库 > 工业防火墙架构与技术【第二节:硬件架构②】

工业防火墙架构与技术【第二节:硬件架构②】

2)、满足对数据包的处理性能的高速度要求

任何防火墙的基本技术功能都是过滤报文。防火墙检查其接收的每个数据包,以确定数据包是否对应于流量模式的所需模板。防火墙然后过滤(丢弃)或转发与这些模板匹配的数据包。这些模板以规则的形式进行建模。在工控防火墙中,有针对已知协议提前建模好的规则模板,也有后期自动学习进行建模的规则模板。由于工控防火墙处理数据包是一个一个处理,包括数据包的校验,数据包每一层包头的处理,所以数据包越小,到达时间就越短,服务器处理数据包要求就越高。比如64B的小包,如果处理数据包要达到线速,那么就要求防火墙67.20纳秒就要处理完一个包,随着物理线路速率越大,处理时间就要求越短,这也就要求服务器硬件和软件都要相应的发展和升级来应对越来越多的数据包处理需求。并且工业环境中各家设备的不同以及使用的工业协议不同,工控防火墙需要同时在工业网络流量中同时并行处理多种工业协议报文。同时,规则库随着时间的增加规则条数也在持续增加,这些都是需要防火墙处理性能的支撑,保障网络数据的传输速度与模式匹配的检测速度满足工业网络的实时性需求。因此,为了考虑工控防火墙对数据包的处理性能以及实时性要求,除了在操作系统层面进行优化设计外,重点考虑在硬件架构设计层面利用硬件加速工控防火墙的处理性能。

一般认为服务器处理能力很强,不是数据包处理的瓶颈,而通过物理线路能够传送数据包的最大速率,即线速(从100Mpbs、1Gbpbs、10Gbpbs、25Gbpbs、40Gbpbs,甚至到100Gpbs)才是网络性能的瓶颈点。当数据包到达防火墙之后,防火墙需要对数据包进行拆包-解析-匹配-过滤-封包-转发的动作。这种动作无疑是整个工业网络线路上的最低速的一环。对于工控防火墙选择何种处理架构是成为工控防火墙乃至工业网络性能影响最为重要的一环。

工控防火墙的处理架构如何能够更快的处理数据包?处理架构是什么?我在这里倾向于理解为“数据从网卡接受数据并通过防火墙内部运作之后再通过网卡传输出去”的这个路径称之为处理架构。这个处理架构包含什么组件,如何运作是我们首先需要明白的问题。

从工控防火墙本身架构来看,这个处理架构包含了:CPU、RAM、主板总线(南北桥或IO桥、PICE)、网卡、网卡控制器。

我们先来说下网卡,网卡作为这个架构的第一道门户,负责数据包的发送和接收。发送流程如下:

1. CPU通知网卡控制器发送内存中的数据;

2. 网卡控制器使用DMA将内存中的数据拷贝到网卡本地内存的发送队列;

3. 网卡的MAC单元等待数据拷贝完成,准备发送;

4. 网卡MAC单元通过PHY(Port Physical Layer)单元将数据的数字信号转换为对应的电信号或光信号从线缆发送出去;

5. 网卡控制器通知CPU数据发送完成。

其接收流程如下:

1. 网卡的PHY单元接收到数据包信号,将其转换为数字信号;

2. 网卡的MAC单元将数据包存储在本地内存的接收队列上;

3. 网卡控制器使用DMA将数据拷贝到系统内存上;

4. 网卡控制器以中断方式告诉CPU数据包已放在了指定的内存空间。

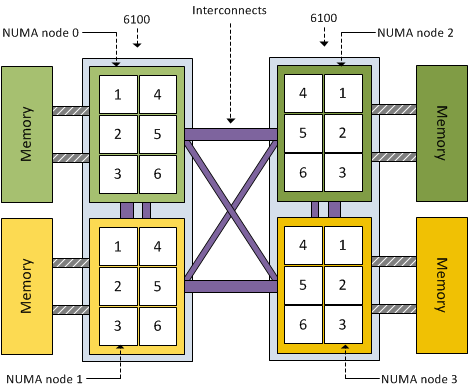

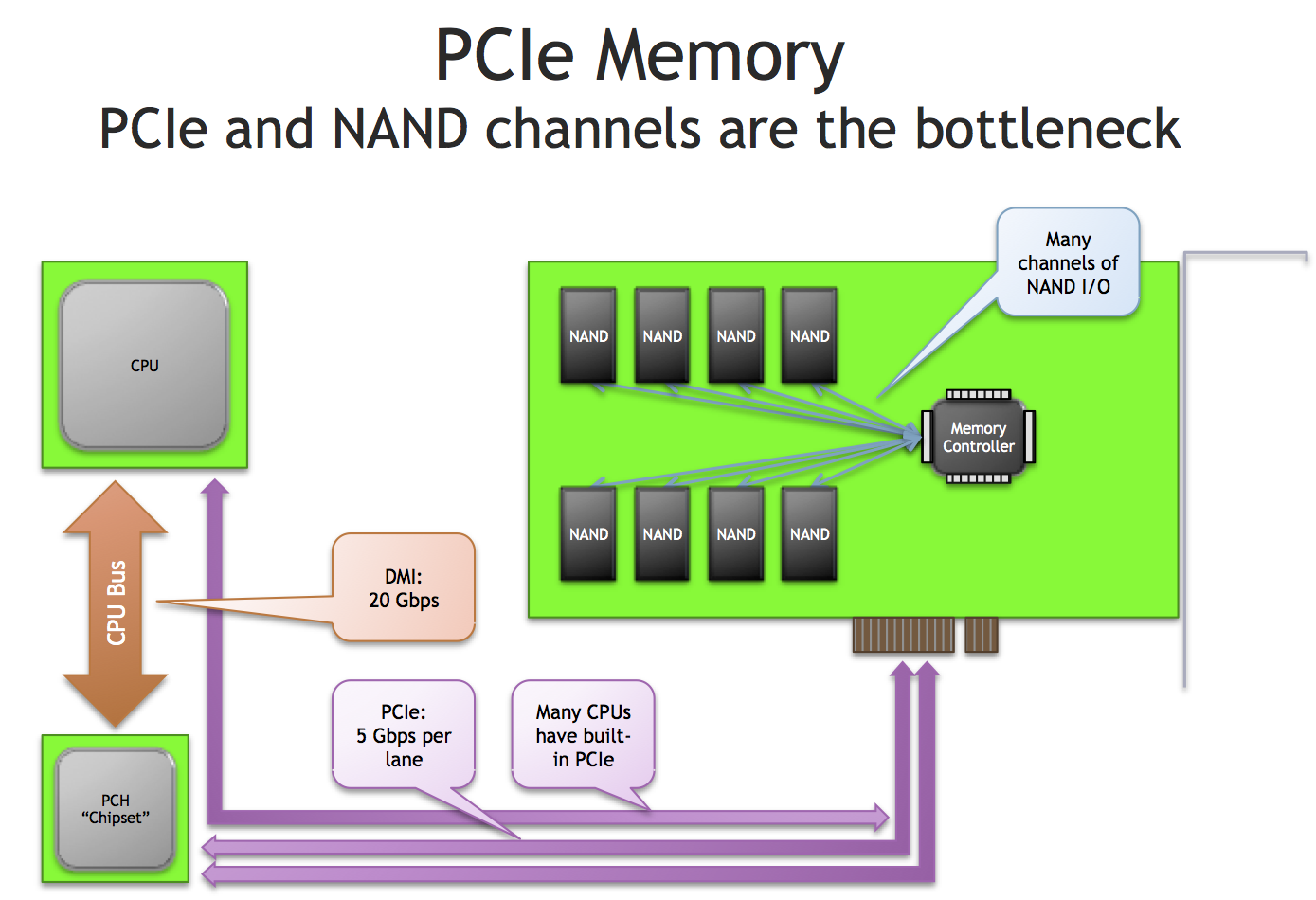

那么网卡位于体系中的位置就显得十分重要,决定着数据包传输路径的长短。网卡最开始集成在主板通过南桥连接,后来网卡插在PCI插槽上,插在PCI-E插槽上,数据包进入网卡后,需要经过南桥(主要管理IO设备),PCI/PCI-E,北桥(主要管理内存),内存和CPU的处理。网卡需要频繁访问内存存取数据包,CPU处理数据包需要频繁访问内存,此时北桥是瓶颈,当CPU个数增加时,单个内存控制器也是瓶颈。为了解决这些瓶颈,就出现了NUMA(Non-UniformMemory Architecture)架构,每个CPU都有自己的内存(将北桥功能集成到了CPU),每个CPU也有直接管理的PCI-E插槽,低速设备比如SATA/SAS,USB等被PCH,Platform Controller Hub(替换了南桥)管理。多核CPU以及NUMA架构使得数据包处理可以以几乎相同处理性能横向扩展,加上网卡的多队列机制,可以实现网络数据包的并发处理。

同时,在这个环节中,随着网卡的网卡控制器(网卡里面的控制器)的更新发展,也对处理架构的性能提升有着重要的影响。目前的网卡控制器都是ASIC(专用集成电路)芯片,该芯片固化了网络的功能,速度快,设计完成后,成本低。但不可编程。现在针对FPGA的网卡控制器越来越流行,FPGA的网卡控制器的好处就是可编程性,具有软件定义网卡的特质,因此是未来发展的方向。ASIC芯片控制器的发展使得网卡的功能越来越强大,之前很多数据包处理的功能都是CPU来完成,占用大量CPU时间,很多重复简单的工作被网卡控制器来处理大大减轻了CPU的负担,这就是网卡Offload功能。网卡的Offload功能会接管原先CPU的部分网络处理功能,比如将TCP,UDP数据包的checksum计算和校验交由网卡处理;将数据包中发送的时候将大数据包的切分为小数据的封装交由网卡处理;同时将接收到的小包合成为一个大包再给到应用程序,这样既减少了CPU的中断,也减少了CPU处理大量包头的负担;除此之外,DMA将内存中的数据包拷贝到网卡内存时,由于内存中的数据包内容在物理内存上是分散存储的,如果没有Offload功能,DMA没法直接拷贝,需要系统kernel拷贝一次数据让地址连续,有了Offload功能,就可以少一次内存拷贝。

因此在这里我们可以得出性能提升的第一个解决方案:NUMA架构+PCIE网卡直连!这种方案也就是多核并行处理。基于这种方案还可以优化的地方在于,网卡的每个队列会对应一个CPU来处理数据包到达的软中断,合理的将网卡队列绑定到指定的CPU能更好的并发处理数据包,比如将网卡队列绑定到离网卡近的CPU上。

这种方案对于处理架构的性能提升是巨大的,但是成本也是最高的。如果考虑到工业环境的硬件需求,这么多的X86 CPU设计出来的产品似乎也很难去适应工业环境的严苛条件。而基于嵌入式的工业主板来说,集成那么多的X86 CPU无风扇显然又是个悖论。并且网卡的处理机制是数据从网卡到CPU之间的传输依靠“中断”实现,当高速网络流量经过时,频繁的“中断”控制导致CPU 占用率迅速上升,防火墙吞吐速率受到严重影响。这也是现今基于X86架构的工控防火墙性能提升存在困难的原因。

那么现在的基于X86架构的工控防火墙是什么架构?现在的X86架构的工控防火墙,其处理架构基于X86 SMP架构和主板上的网卡位置(南桥/PCI/PCI-E),其处理速度基于网卡位置而不同,位于南桥最慢,位于PCIE最快。不过现在南桥基本上从主板上消失,因此主流的是PCI和PCIE。

根据上述论述我们知道,处理架构到这里,处理器成为了瓶颈。X86的处理架构应用于工控防火墙具有不可弥补的缺陷,因此市面上就有了基于其他处理器构造工控防火墙的处理架构的方案。比如利用ASIC架构、NP架构、FPGA架构、ARM架构以及MIPS架构等。为了工控防火墙性能,处理器的选择也是百花齐放了,比如说就现在国内市面上的工控防火墙调研来看,大部分采用的是基于X86架构,比如力控华康的工控防火墙就是X86架构;少数部分厂商采用MIPS架构,比如威努特的工控防火墙就是基于MIPS架构。其他的处理器方案,ASIC架构是国外厂家采用最多的方案,基于ASIC架构的防火墙从架构上改进了中断机制,数据通过网卡进入系统后,无需经过主CPU处理,而是由集成在系统中的芯片直接处理,完成防火墙的功能,如路由、NAT、防火墙规则匹配等。还有一种是采用NP架构,网络处理器(Network Processor,简称NP)架构是传统防火墙采用的设计方案之一,也可以平滑的迁移到工控防火墙领域。其特点是综合了X86和ASIC的优缺点,采取一个折中的平衡方案。采用NP架构的防火墙,各种算法可以通过硬件实现,在实现复杂的拥塞管理、队列调度、流分类和QoS功能的前提下,还可以达到极高的查找、转发性能,实现“硬转发”。

从这些处理器来说,各自构建的防火墙的各有优劣,X86架构的优点是灵活性高,扩展性好,应用层的处理速度要比MIPS架构好。缺点是性能差,小包速率低(30%-40%)。ASIC架构的优点是性能高。缺点是灵活性低,扩展性差,开发费用高,开发周期长。MIPS架构是目前最为看好的架构,其多核架构,被认为是解决信息安全产品功能与性能之间矛盾的一大硬件法宝。其针对嵌入式的多核处理器架构,也被认为是解决工控安全产品功能与性能之间矛盾的硬件法宝。多核是在同一个硅晶片上集成了多个独立物理核心,每个核心都具有独立的逻辑结构,包括缓存、执行单元、指令级单元和总线接口等逻辑单元,通过高速总线、内存共享进行通信。在实际工作中,每个核心都可以达到2Ghz以上的主频。因此,多核技术无论在性能、灵活性还是在开发的成本和难度方面,都是其他架构不能比拟的。目前Cavium 公司提供的MIPS64架构的Cavium 处理器核心数最多可以达到48核。MIPS自身系统的软件平台较为落后,如果你们公司拥有足够的技术研发力量,可以考虑采用MIPS架构作为工控防火墙的处理器。

本文出自 “我拿流年乱了浮生” 博客,请务必保留此出处http://tasnrh.blog.51cto.com/4141731/1918455

工业防火墙架构与技术【第二节:硬件架构②】