首页 > 代码库 > 加法器

加法器

加法机

一、全加器

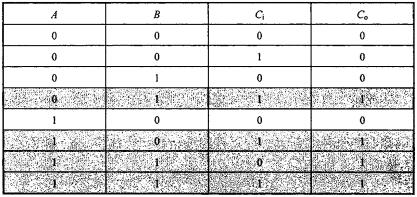

在上图中,A和B分别是来自被加数和加数的一个比特,它们正好在同一列上;Ci是来自右边一列的进位;Co是本列产生的进位;S是本列的“和”。

全加器的复杂之处在于,当它被连接到一个电路中的时候,不知道A、B和Ci将会是什么,它们是0还是1。所以,根据实际的情况来安排响应的输出,这就是全加器存在的价值和意义。经过仔细分析,三个比特(A、B和Ci)相加,有8种可能的情况,分别是:

0 + 0 + 0

0 + 0 + 1

0 + 1 + 0

0 + 1 + 1

1 + 0 + 0

1 + 0 + 1

1 + 1 + 0

1 + 1 + 1

全加器操纵的是0和1,初次之外别无他物。这意味着,如果你把它和逻辑的真假、开关的闭合与断开相比较的话,很相似。这样,如果要构造全加器,从这些特定的输入得到合适的输出结果,开关电路是个不错的选择。

全加器输出端S的真假值表

全加器进位Co的真值表

根据学习的逻辑学和逻辑电路的知识,为了从真值表得到逻辑表达式,实际上我们只需要考虑那些输出为“1”的行,也就是上面两张表中颜色较深的那些行。这样,把上表那些使得S为1的行挑出来,写出逻辑表达式:

S=A‘B‘Ci + A‘BC‘ + AB‘C‘ + ABCi

接着,把那些使得进位Co为1的行也挑出来,也写出逻辑表达式:

Co =A‘BCi + AB‘Ci + ABCi‘ + ABCi

上面从根本上解决了制造一个全加器所需要的所有技术,使用的都是最基本的逻辑门电路。

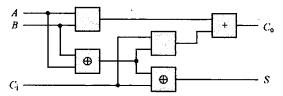

全加器结构

上面全加器设计简化后的设计如下图:

二、加法机

把所有的全加器连接在一起、封装到一起的时候,我们就会看到一个完整的加法机。

有了全加器,解决了二进制加法过程中每一列的计算问题,那么,我们可以搞一大堆全加器,根据被加数和加数的比特数,把它们串联起来组成一个完整的加法电路。

本文出自 “德泽无忧” 博客,请务必保留此出处http://dezewuyou.blog.51cto.com/2628602/1903360

加法器